# Departments of ECE and CISE

#### Introduction

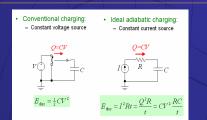

The key barrier that in the past has prevented adiabatic ( thermodynamically reversible) logic-circuit design techniques from becoming a practical approach for ultralow-power digital computing is the lack of energy efficiency in the power supply, due to the low Q factors of AC signal generators that can be built using standard integrated electronics.

# $\begin{array}{c} \mathbf{x} & \mathbf{y} \\ \mathbf{x} & \mathbf{x} \\ \mathbf{x} & \mathbf{y} \\ \mathbf{x} & \mathbf{x} \\ \mathbf{x} & \mathbf$

#### **Current Research**

In the ADIAMEMS project at the University of Florida, we are designing a custom MEMS resonator for driving fully-adiabatic pipelined logic based on the 2LAL (two-level adiabatic logic) family previously developed at UF. The resonator design is being optimized so as to maximize its effective Q factor and area efficiency, at an operating frequency chosen to maximize the power-performance of the adiabatic logic.

Use a voltage ramp to approximate

- Through the same, or a different path.

Can discharge the load later using a similar ramp.

Adiabatic vs. Conventional Power vs. Frequency

$t \gg RC \Rightarrow E_{diss} \rightarrow CV^2 \frac{RC}{t} \quad t \ll RC \Rightarrow E_{diss} \rightarrow \frac{1}{2}CV^2$

Input parameters for an example scenario

Adia./Conv. Time

Min. Relative Time

an ideal current source.

$V_{\circ} > V + V_{\rm T}$  during ramp.

o wor

Switch conditionally, V{ if MOSFET gate voltage

Advantage factor A = ½CV2/(CV2RC/t) = t/2RC

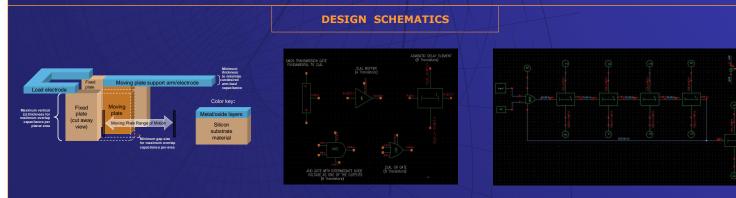

# ADIABATIC LOGIC DESIGN

- Avoiding passing current through diodes

- Never turn on a transistor when V<sub>DS</sub> ≠ 0

- Never turn off a transistor when  $I_{DS} \neq 0$

- "The logic design must be logically reversible"

- Leakage Power should be kept Manageable

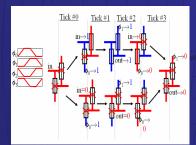

In tick 0, the input transitions to 1 (at the same time as  $\Phi_0$ ), and the output switch turns on.

In tick 1,  $\Phi_1$  goes high (unconditional bias) taking the output with it. This turns on the reverse switch.

•In tick 2, the input is retracted from its source, turning off the output switch .The output information is latched into place.

•In tick 3  $\Phi_0$  reverts to its low state which does not affect anything inside the circuit but prepares us to be able to turn on the forward switch again in the next cycle. Meanwhile, the next gate in the chain restores the output to the zero level.

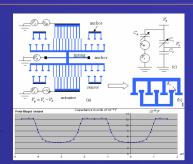

### MEMS RESONATOR DESIGN

## •Figure (a) The resonator design.

•Figure (b) The sensing structure composed of comb fingers with a wide portion at the end. This unusual comb finger geometry is used to create a non-sinusoidal waveform when the resonator oscillates sinusoidally.

•Figure (c) The sensor position when the resonator beam oscillates to the maximum amplitude position.

-Symbols: V<sub>b</sub>=resonator bias, V<sub>c</sub>=DC actuator bias ,v<sub>ac</sub>=amplitude of AC actuator bias, C<sub>a</sub>, C<sub>s</sub>, C<sub>l</sub>=actuator/sense/load capacitances.

1E-03 1E-04 1E-05 1. vdown Factor RC /t

•In the AdiaMEMS project at UF, we are taking the first steps towards demonstrating adiabatic techniques that can actually be commercially practical for ultra-low-power logic.

A prototype MEMS resonator producing a high quality custom wave shape was successfully designed and sent out for fabrication. Simulations on new 2LAL design style indicate that a 50× performance boost might be achieved versus conventional CMOS in ultra-low-power application scenarios in a presently available process technology.

Regarding the future promise of adiabatics, we can declare: "You ain't seen nothin' yet"

# Spring beams Actuation comb

The 3D model of the complete resonator design presently being fabricated

Principal Investigators: Dr Michael P Frank , Dr Huikai Xie Graduate Students: Uma Aghoram , Venkiteswaran Anantharam , Maojiao He , Krishna Natarajan